Veri-Sure:正しいRTLコード生成のための時間的追跡と形式検証を備えた契約認識型マルチエージェントフレームワーク

大規模言語モデルを用いたRTL設計において、設計契約(Design Contract)を核としたマルチエージェントフレームワーク「VERI-SURE」を開発し、エージェント間での意図の乖離(セマンティック・ドリフト)を防ぐ仕組みを構築しました。

TL;DR(結論)

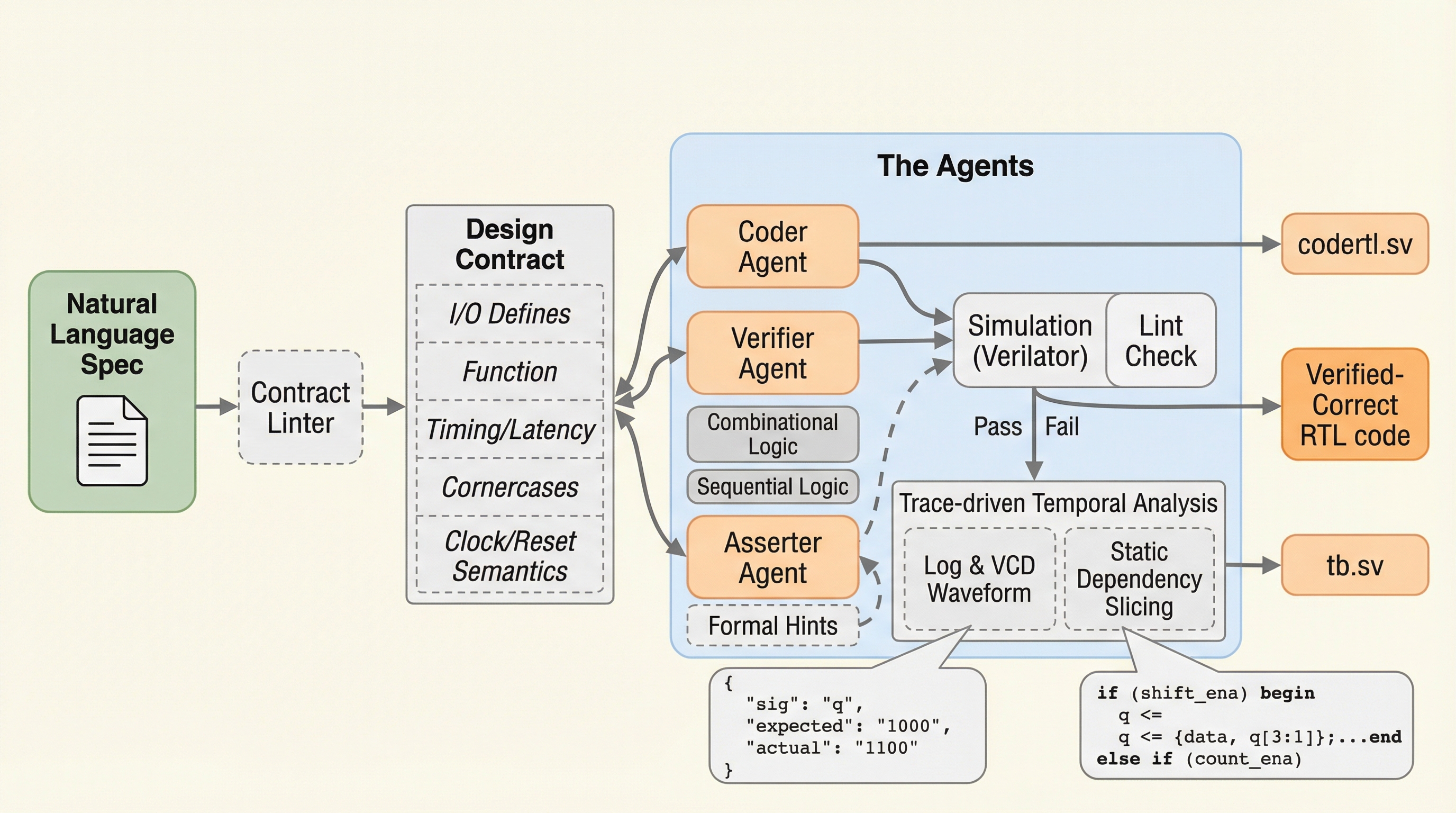

大規模言語モデルを用いたRTL設計において、設計契約(Design Contract)を核としたマルチエージェントフレームワーク「VERI-SURE」を開発し、エージェント間での意図の乖離(セマンティック・ドリフト)を防ぐ仕組みを構築しました。 波形解析に基づく時間的診断と静的依存関係スライシングを組み合わせることで、エラー箇所を特定して局所的に修正するパッチ適用メカニズムを導入し、ファイル全体の再生成に伴う回帰バグやハルシネーションを効果的に抑制することに成功しました。 産業グレードの課題53件を追加した拡張ベンチマーク「VERILOGEVAL-V2-EXT」において、シミュレーションと形式検証を統合したパイプラインにより、従来のモデルやエージェントシステムを凌駕する、世界最高水準の正確性と信頼性を達成しました。

なぜこの問題か

電子設計自動化(EDA)の分野では、チップ設計の複雑化に伴い、レジスタ転送レベル(RTL)の記述を自然言語から自動生成する大規模言語モデル(LLM)の活用が強く期待されています。しかし、ハードウェア記述言語(HDL)は一般的なソフトウェアプログラミングとは本質的に異なり、厳密なサイクル精度のタイミング、高度な並列動作、複雑な通信プロトコルのセマンティクス、および階層的な構造制約を伴うため、既存のモデルでは正確な生成が極めて困難です。一般的なコーディングモデルは、構文的には正しいVerilogコードを出力できたとしても、ハードウェア特有の時間的な意図やグローバルな構造の一貫性を維持できず、特に複雑なタイミングが絡むコーナーケースで失敗することが多いのが現状です。 現在のLLMベースのRTL生成パイプラインには、主に3つの致命的なボトルネックが存在しています。第一に、シミュレーション中心の評価ではテストカバレッジが限定的であり、稀にしか発生しないタイミングエラーやコーナーケースでの違反を見逃すリスクが常に付きまといます。…

核心:何を提案したのか

本研究では、設計契約(Design Contract)をエージェント間の「共有の真実」として定義し、時間的追跡と形式検証を組み合わせたマルチエージェントフレームワーク「VERI-SURE」を提案しました。このフレームワークは、自然言語の仕様をまず構造化されたJSON形式の設計契約へと蒸留します。この契約には、モジュールのインターフェース、クロックとリセットの規則、各出力のレイテンシ、コーナーケースを含む機能概要、およびテスト計画が明文化されており、設計の全工程を通じてエージェントの意図を整列させる役割を果たします。これにより、曖昧な自然言語から生じる解釈の齟齬を排除し、一貫した設計フローを実現しました。…

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related