SINA:人工知能を用いた回路図画像からネットリストへの生成器

SINAは、回路図の画像からSPICE互換のネットリストを全自動で生成するオープンソースの革新的なパイプラインであり、深層学習と高度な画像処理技術を統合することで、従来の手法が抱えていた素子認識の誤りや複雑な接続推論の困難さといった課題を根本から解決することに成功した。

TL;DR(結論)

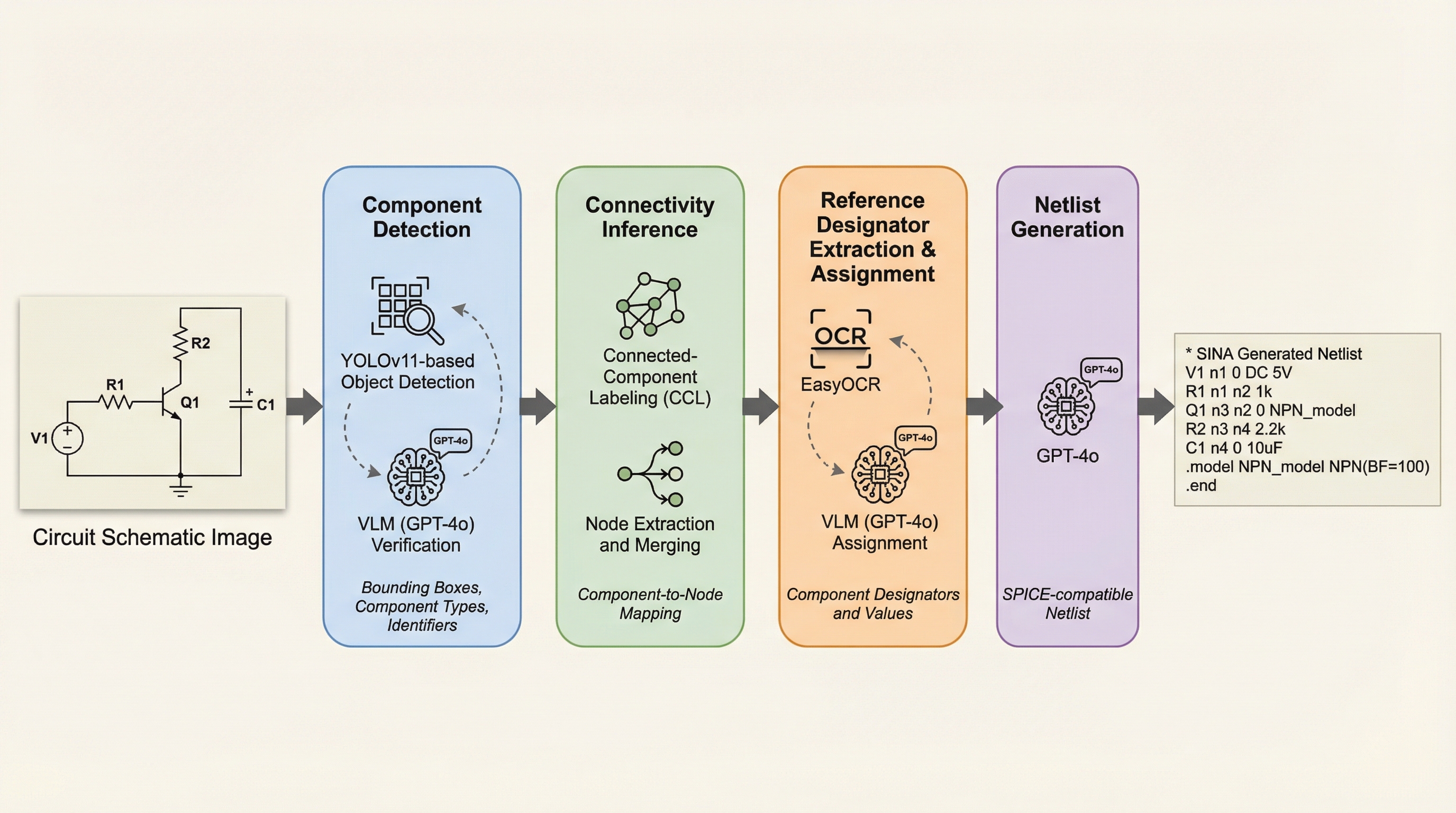

SINAは、回路図の画像からSPICE互換のネットリストを全自動で生成するオープンソースの革新的なパイプラインであり、深層学習と高度な画像処理技術を統合することで、従来の手法が抱えていた素子認識の誤りや複雑な接続推論の困難さといった課題を根本から解決することに成功した。 具体的な仕組みとして、YOLOv11を用いた高精度な素子検出、連結成分ラベル付け(CCL)による正確な配線解析、そしてEasyOCRと視覚言語モデル(VLM)であるGPT-4oを組み合わせた参照指定子の割り当てプロセスを導入しており、多様な描画スタイルや低品質な画像に対しても極めて堅牢な動作を実現している。 評価実験では96.47%という驚異的なネットリスト生成精度を達成し、既存の最先端手法であるMasala-CHAIと比較して約2.72倍という圧倒的な性能向上を示しており、アナログ回路設計のデジタル化やAI学習用データセットの構築を劇的に加速させる基盤技術として期待されている。

なぜこの問題か

近年の人工知能、特に大規模言語モデル(LLM)の急速な進歩は、デジタル回路設計のワークフローに劇的な革新をもたらしているが、アナログおよびミックスドシグナル設計の分野ではその恩恵が極めて限定的であるという深刻な課題がある。 この主な原因は、既存の膨大な回路知識が電子設計自動化(EDA)ツールで直接扱える機械可読な形式で十分に存在しないことにあり、研究論文や教科書、ウェブサイトに掲載されている検証済みの回路図の多くは画像形式のままで保存されている。 現在のEDAワークフローにおいて、これらの回路図画像からネットリストを作成する作業は依然として設計者による手作業に依存しており、このプロセスは極めて低速で人為的なミスが発生しやすく、AIモデルの学習に不可欠な大規模データセットの構築を妨げる大きな要因となっている。 既存の自動化ツールもいくつか提案されてはいるものの、素子の認識精度が不十分であったり、複雑な配線の接続関係を正しく推論できなかったり、あるいは素子の名前や値といった参照指定子の抽出と割り当てが不正確であるといった致命的な制限を抱えている。…

核心:何を提案したのか

本論文では、回路図画像からSPICE互換のネットリストを生成するための、オープンソースかつ完全に自動化されたパイプラインである「SINA」を提案しており、これは多様な回路図のスタイルに対して堅牢に動作するように設計されている。 SINAの核心的な提案は、複数のAI技術と画像処理アルゴリズムを独自のワークフローで統合した点にあり、素子認識のためのYOLOv11ベースの検出器、接続推論のための連結成分ラベル付け(CCL)、テキスト抽出のための光学文字認識(OCR)、そして文脈に基づいた割り当てを行う視覚言語モデル(VLM)を組み合わせている。…

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related