EvolVE:LLMベースのVerilog生成と最適化のための進化的探索

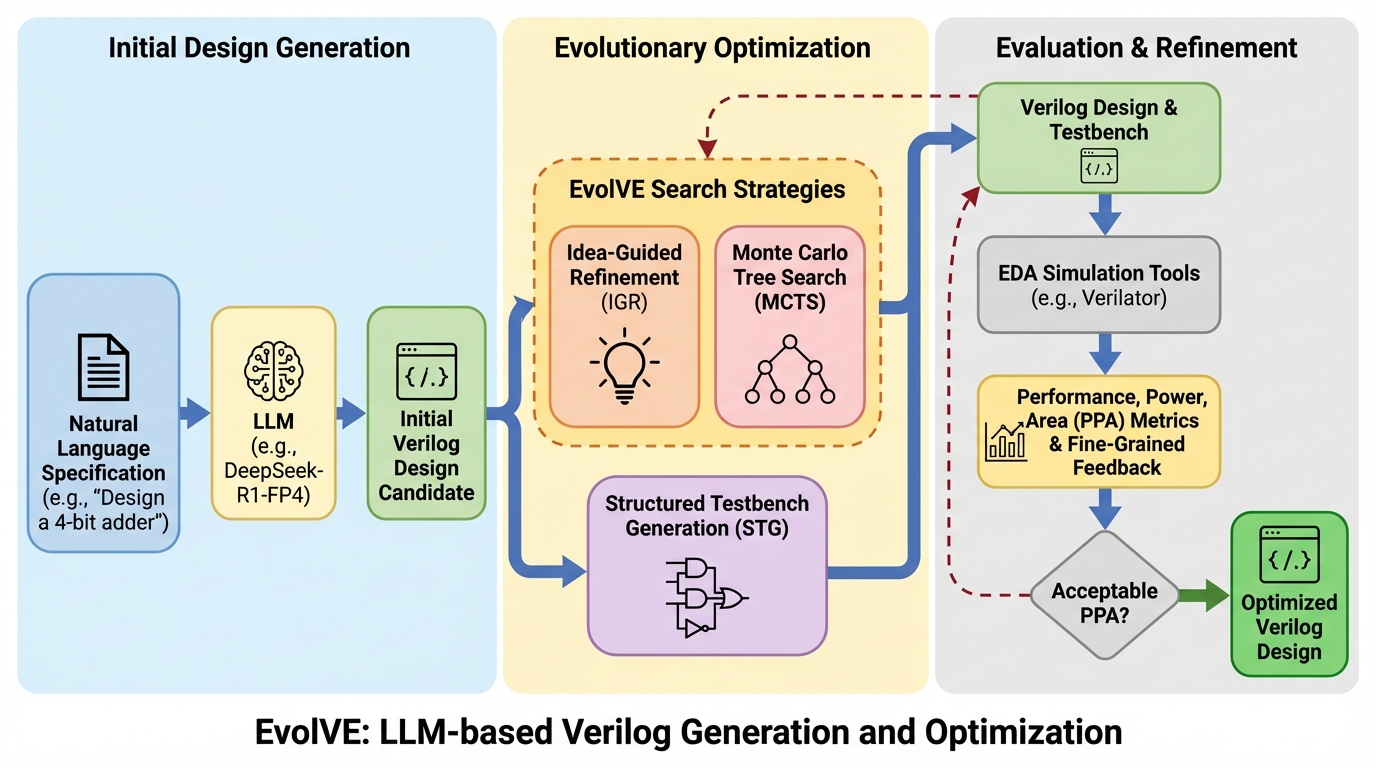

EvolVEは、大規模言語モデル(LLM)を活用してハードウェア記述言語であるVerilogのコード生成と最適化を自動化する、進化的探索アルゴリズムに基づいた革新的なフレームワークである。 機能的正当性を最大化するモンテカルロ木探索(MCTS)と、設計の最適化に特化したアイデア主導型洗練(IGR)という二つの異なる戦略を使い分け、さらに検証プロセスを高速化する構造化テストベンチ生成(STG)を導入している。 評価の結果、既存のベンチマークで世界最高水準の正解率を達成しただけでなく、産業規模の課題を含むIC-RTLベンチマークにおいて、人間による設計を大幅に上回る電力・性能・面積(PPA)の削減に成功した。

TL;DR(結論)

EvolVEは、大規模言語モデル(LLM)を活用してハードウェア記述言語であるVerilogのコード生成と最適化を自動化する、進化的探索アルゴリズムに基づいた革新的なフレームワークである。 機能的正当性を最大化するモンテカルロ木探索(MCTS)と、設計の最適化に特化したアイデア主導型洗練(IGR)という二つの異なる戦略を使い分け、さらに検証プロセスを高速化する構造化テストベンチ生成(STG)を導入している。 評価の結果、既存のベンチマークで世界最高水準の正解率を達成しただけでなく、産業規模の課題を含むIC-RTLベンチマークにおいて、人間による設計を大幅に上回る電力・性能・面積(PPA)の削減に成功した。

なぜこの問題か

デジタルハードウェアの複雑さが指数関数的に増大する中で、半導体業界は回路性能を犠牲にすることなく開発サイクルを短縮するという極めて困難な課題に直面している。Verilogのようなハードウェア記述言語(HDL)は、同期回路のきめ細かな制御を可能にする業界標準の言語であるが、手動によるRTLコーディングは極めて労働集約的であり、開発プロセス全体の大きなボトルネックとなっている。近年、大規模言語モデル(LLM)が自動化の有望な手段として注目されているが、ハードウェア設計特有の厳格な形式論理や並行性を正確に捉えることが難しいという本質的な問題がある。LLMは基本的に逐次的な推論を得意とする確率モデルであり、数千の操作がクロック信号に同期して並列に実行されるVerilogの並行システムをモデル化することに苦労する。その結果、LLMをHDL生成に直接適用しても、機能的に不正確であったり、物理的に合成不可能なコードが出力されたりすることが非常に多い。 また、ハードウェアドメイン固有の高品質なトレーニングデータがソフトウェア言語に比べて圧倒的に不足していることや、固定されたモデル容量による推論の限界も、自動生成の大きな障壁となっている。…

核心:何を提案したのか

本研究では、LLMベースのVerilog生成と最適化を飛躍的に向上させるための進化的探索フレームワークである「EvolVE」を提案した。このフレームワークの最大の特徴は、モデルの追加学習やファインチューニングを一切必要とせず、進化的アルゴリズムを活用して設計の探索とデバッグを高度に統合している点にある。具体的には、設計の目的に応じて使い分けが可能な二つの異なる探索戦略、すなわち「アイデア主導型洗練(IGR)」と「モンテカルロ木探索(MCTS)」を導入した。研究チームの分析により、MCTSは機能的な正当性を極限まで高めることに優れており、一方でIGRは設計の最適化において極めて優れた性能を発揮することが明らかになった。これにより、論理的に正しい回路を作る段階と、その回路をより効率的に磨き上げる段階の両方で最適な探索が可能となった。…

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related