ChipBench: AIチップ設計支援におけるLLM性能評価のための次世代ベンチマーク

既存のAIチップ設計ベンチマークは単純なモジュールに限定され、最新の大規模言語モデル(LLM)が95%以上の成功率を達成するなど飽和状態にあり、実務の複雑な階層構造や設計の機微を評価できていない。

TL;DR(結論)

既存のAIチップ設計ベンチマークは単純なモジュールに限定され、最新の大規模言語モデル(LLM)が95%以上の成功率を達成するなど飽和状態にあり、実務の複雑な階層構造や設計の機微を評価できていない。 本研究が提案するChipBenchは、44個の複雑な階層モジュール、89個のデバッグ事例、132個のリファレンスモデル評価用サンプルを備え、Verilog生成、デバッグ、リファレンスモデル作成の3タスクを包括的に網羅する。 検証の結果、最新のClaude-4.5-opusでもVerilog生成で30.74%、Pythonリファレンスモデル生成で13.33%の成功率に留まり、既存の評価指標では見えなかったLLMの限界と実用化に向けた課題が浮き彫りになった。

なぜこの問題か

現代の半導体エンジニアリングにおいて、大規模言語モデル(LLM)はコード生成や対話型AIとして大きな可能性を示しているが、既存の評価指標には産業界の実態を反映していないという決定的な欠陥が3点存在する。第一に、既存のVerilogEvalやRTLLMなどのベンチマークは、モデルの急速な進歩により、最新の生成システムが95%以上の精度を達成するなど、すでに評価尺度としての機能を失いつつある。これらのタスクは10行から76行程度の極めて単純な機能モジュールに限定されており、実際の設計で不可欠な階層構造やモジュール間の相互作用が含まれていない。産業用Verilogは通常1万行を超え、複雑な再利用や検証システムを伴うが、既存のデータセットは競技プログラミング由来のものが多く、実務のコードスタイルとは大きく乖離している。 第二に、既存の評価はコード生成のみに偏重しており、チップ設計においてより重要かつ実用的なデバッグ能力の評価が欠落している。設計ミスは数十億ドルの損失を招く可能性があるため、企業はLLMによる完全な自動生成よりも、既存ワークフローに組み込みやすいデバッグ支援を求めている。…

核心:何を提案したのか

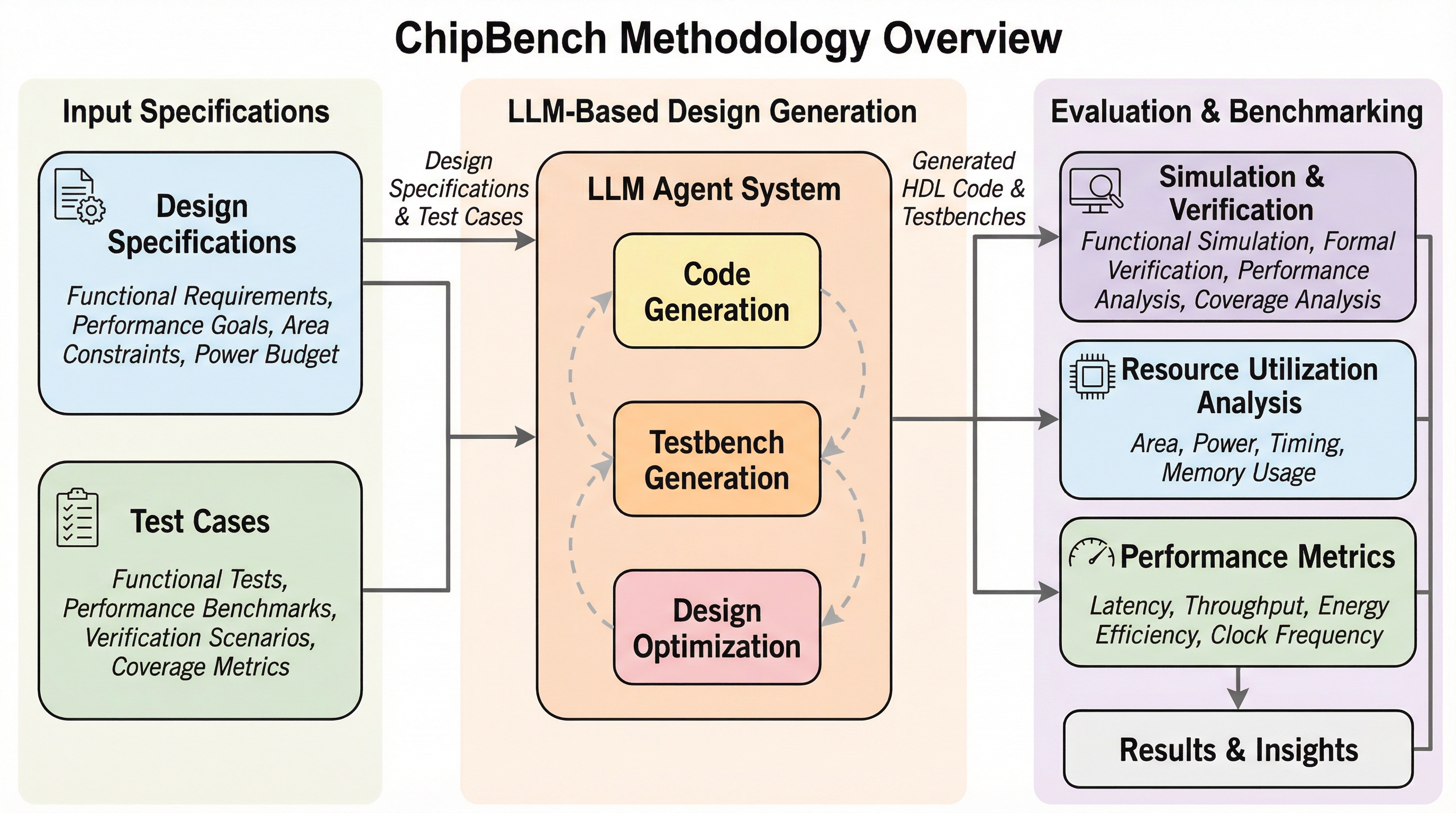

本研究は、チップ設計の全工程を網羅的に評価するために、新たなベンチマークであるChipBenchを提案した。ChipBenchは、単なるコード生成のテストを超え、デバッグやリファレンスモデル生成を含むチップ設計ワークフローの多角的な評価を可能にする。具体的には、オープンソースのCPU IPや競技プラットフォームから厳選された44個の高品質なVerilogモジュールを収録している。これらは自己完結型モジュール、非自己完結型の階層構造モジュール、そして実際のCPUサブモジュールの3つのカテゴリに分類される。ChipBenchのデータセットは、先行研究であるVerilogEvalと比較して、コードの平均長で3.8倍、セル数で13.9倍という圧倒的な複雑さを備えている。…

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related