OSIRIS: スケーラブルなデータセット生成によるアナログ回路設計と機械学習の橋渡し

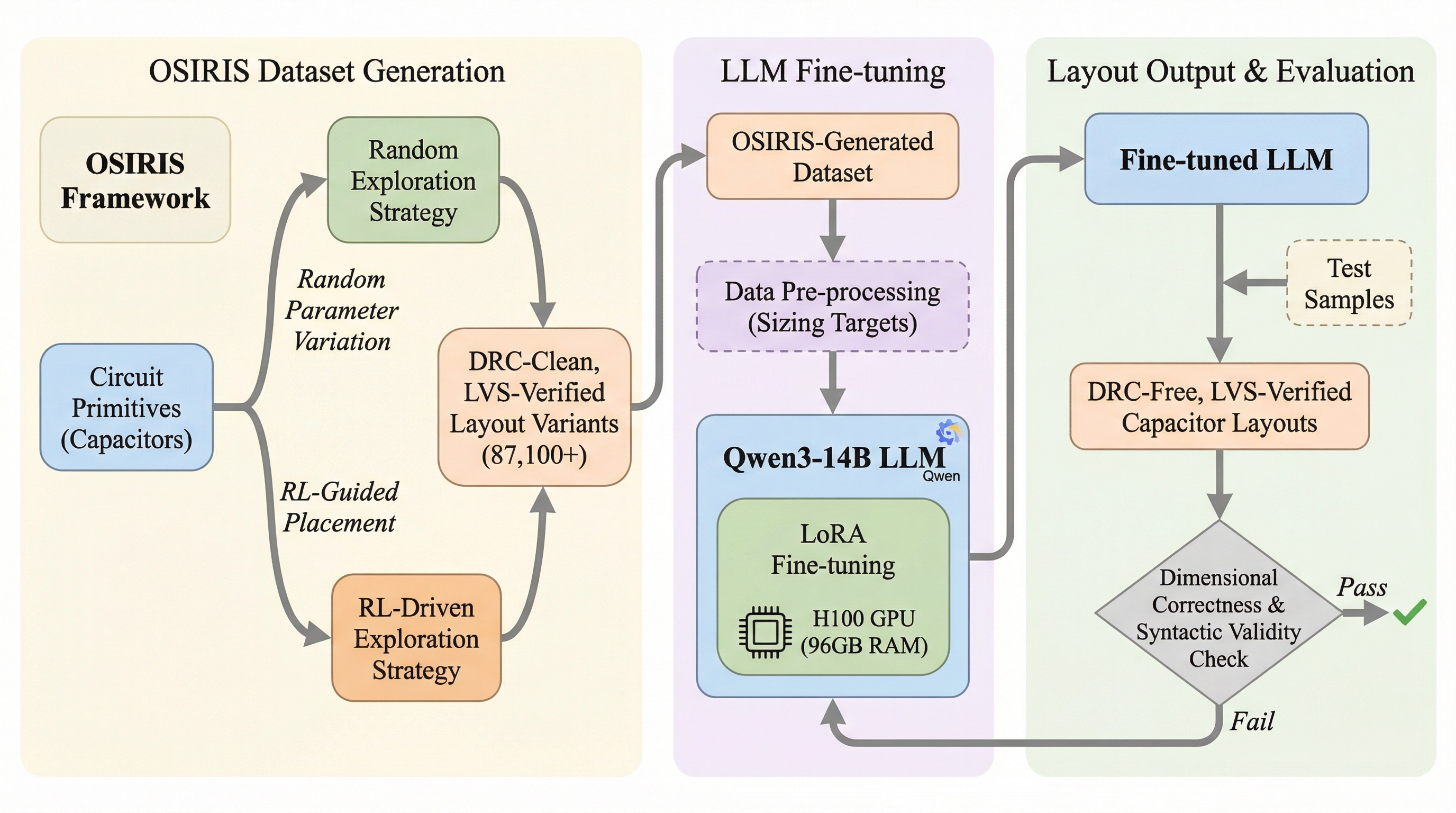

アナログ集積回路(IC)のレイアウト設計は、物理的な配置や寄生効果、回路性能の複雑な相互依存関係により、依然として手動作業が中心の困難な課題となっています。本研究では、アナログIC設計のためのスケーラブルなデータセット生成パイプラインである「OSIRIS」を提案し、設計空間を体系的に探索して包括的な性能指標とメタデータを生成する手法を確立しました。このフレームワークを用いて生成された87,100個の回路バリエーションを含むデータセットを公開し、強化学習を用いたレイアウト最適化や大規模言語モデルの微調整による自動生成の可能性を実証しています。

TL;DR(結論)

アナログ集積回路(IC)のレイアウト設計は、物理的な配置や寄生効果、回路性能の複雑な相互依存関係により、依然として手動作業が中心の困難な課題となっています。本研究では、アナログIC設計のためのスケーラブルなデータセット生成パイプラインである「OSIRIS」を提案し、設計空間を体系的に探索して包括的な性能指標とメタデータを生成する手法を確立しました。このフレームワークを用いて生成された87,100個の回路バリエーションを含むデータセットを公開し、強化学習を用いたレイアウト最適化や大規模言語モデルの微調整による自動生成の可能性を実証しています。

なぜこの問題か

現代の電子機器において、アナログ集積回路は通信、電力、オーディオ、バイオメディカル、計測機器などの幅広い分野で極めて重要な役割を担っています。これらはデジタルシステムと物理環境を繋ぐ架け橋として、精密なセンシング、増幅、フィルタリングを可能にし、堅牢なデータ取得と信号処理を実現します。しかし、デジタルIC設計が高度に自動化され、機械学習の導入が進んでいるのに対し、アナログ回路の設計は依然としてその多くが熟練の設計者による手動作業に依存しています。この背景には、アナログ設計特有の複雑さと感度の高さという二つの大きな要因が存在します。 第一に、デジタル設計が単純な論理ゲートに基づいているのに対し、アナログ回路はMOSFET、抵抗器、コンデンサといった多様なコンポーネントを使用し、それらが複雑に相互接続されています。第二に、アナログ回路は非常に感度が高く、物理的なレイアウトのわずかな変更が回路の機能や性能に劇的な影響を及ぼす可能性があります。…

核心:何を提案したのか

本研究では、アナログIC設計におけるバックエンド自動化と機械学習研究を促進するために、スケーラブルなデータセット生成パイプラインである「OSIRIS」を提案しました。OSIRISは、従来のシングルパスの自動化手法とは異なり、性能駆動型の反復的なレイアウト設計空間探索を可能にするエンドツーエンドのフレームワークです。このシステムは、回路の論理的な機能を維持したまま、物理的な実装のバリエーションを大量に生成し、それぞれの性能を評価する機能を備えています。 OSIRISの主な貢献は三つの点に集約されます。第一に、一般的なアナログ回路に対して、DRCを遵守しLVS検証済みのレイアウトを数万規模で効率的に生成、検証、評価するパイプラインを構築したことです。本研究ではその能力を示す例として、87,100個のレイアウトを含むデータセットを生成し、公開しました。…

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related