確率的焼きなまし法のメモリ効率的なFPGA実装

組合せ最適化問題を高速に解く手法として期待される確率的シミュレーテッドアニーリング(SSA)において、ハードウェア実装時の課題であった膨大なメモリ使用量を削減するため、中間状態の保存タイミングを最適化したHA-SSAアルゴリズムが提案されました。

TL;DR(結論)

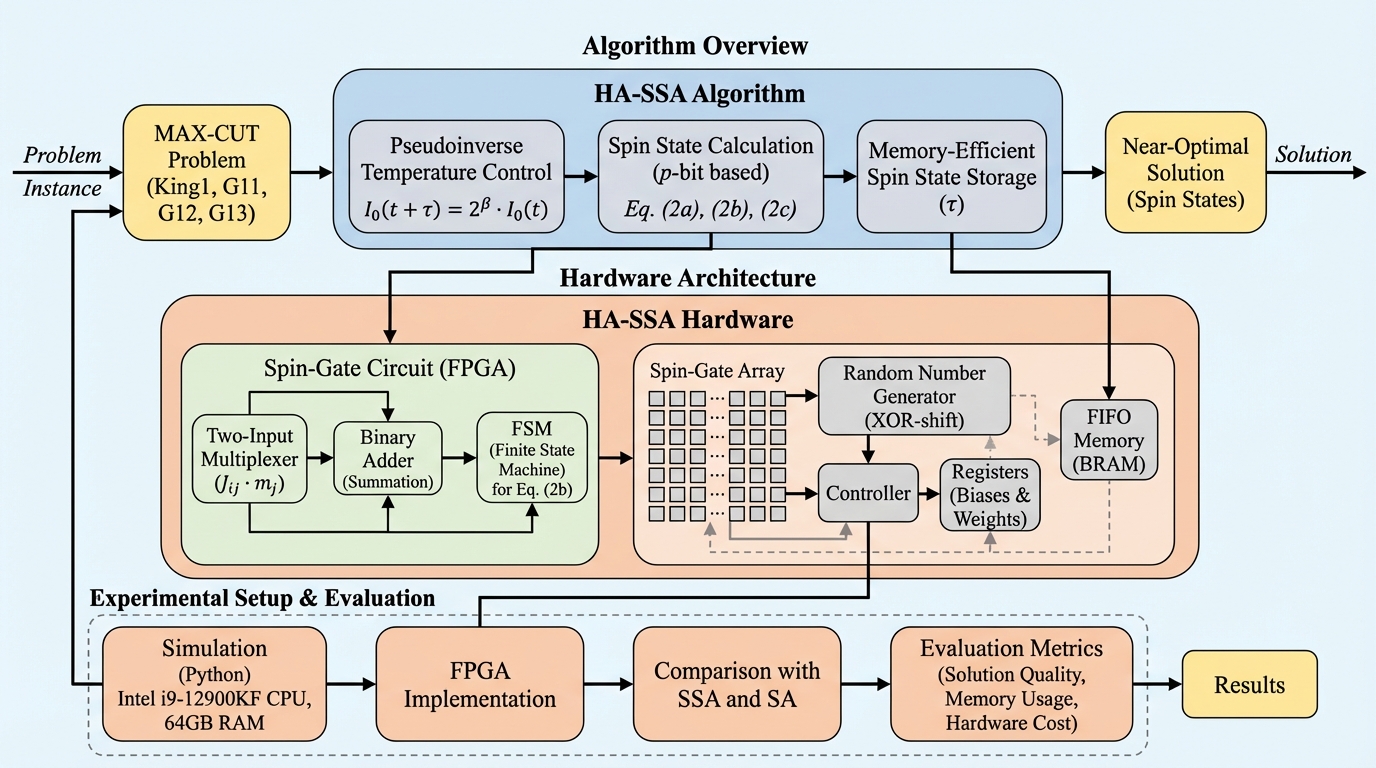

組合せ最適化問題を高速に解く手法として期待される確率的シミュレーテッドアニーリング(SSA)において、ハードウェア実装時の課題であった膨大なメモリ使用量を削減するため、中間状態の保存タイミングを最適化したHA-SSAアルゴリズムが提案されました。 この手法は、温度制御に浮動小数点演算を必要としない整数演算とビットシフトを採用することで回路コストを抑制し、従来のSSAと比較して最大6倍のメモリ効率を実現しながら、最適解に近い解を導き出す能力を維持しています。 Xilinx Kintex-7 FPGAを用いた検証では、最大カット問題において従来のシミュレーテッドアニーリング(SA)より最大114倍高速に収束し、並列テンパリングを用いた既存のソルバーに対しても約2.6倍の計算速度向上を達成しました。

なぜこの問題か

組合せ最適化問題は、膨大な選択肢の中から最適な組み合わせを特定する課題であり、移動ロボットの経路計画や大規模集積回路(VLSI)の設計など、現代社会の多様な分野で極めて重要な役割を果たしています。シミュレーテッドアニーリング(SA)は、これらの問題に対して近似的な最適解を見つけ出すための強力な確率的アルゴリズムとして広く利用されてきました。しかし、SAには致命的な弱点があり、扱う問題の規模が大きくなるに従って、解を得るために必要な計算時間が急激に増大するという性質を持っています。この計算時間の増大は、大規模な実問題を解決する上での大きな障壁となっており、計算を加速させるための新しいコンピューティング手法が切実に求められてきました。 近年、この課題を解決するアプローチとして、量子アニーリングや確率的シミュレーテッドアニーリング(SSA)といった非従来型の計算手法が注目を集めています。SSAは、組合せ最適化問題をイジングモデルと呼ばれるネットワーク構造に変換し、確率的ビット(p-bit)を用いてスピンの状態を表現することで、従来のSAよりも高速な収束を実現できることが報告されています。…

核心:何を提案したのか

本研究では、FPGA実装におけるメモリ効率を劇的に向上させることを目的とした、ハードウェアを意識した確率的シミュレーテッドアニーリング(HA-SSA)アルゴリズムを提案しています。このHA-SSAの最大の特徴は、計算の過程で生成される中間結果のすべてを保存するのではなく、特定の条件下でのみスピン状態をメモリに格納するという戦略を採用した点にあります。具体的には、擬似逆温度が最大値に達したタイミングでのみスピン状態を保存するように設計されており、これにより計算精度を維持したまま、メモリの使用量を大幅に削減することに成功しました。 また、HA-SSAはハードウェア実装時の演算コストを最小化するための工夫も取り入れています。…

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related