ゼロ調整で多コーナ歩留まり解析を回す:学習済み事前分布で Tuning Barrier を越える

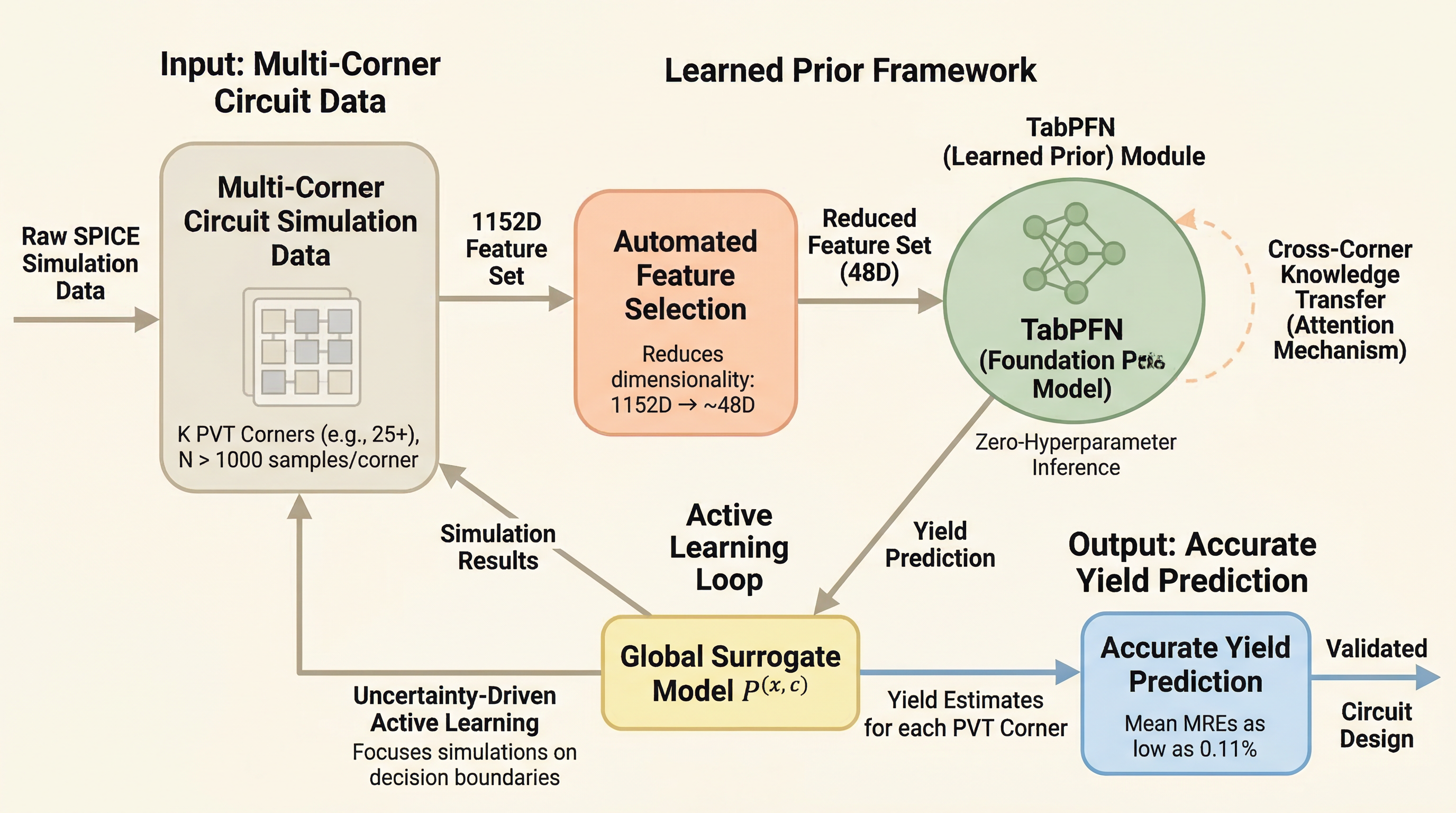

25以上の Process-Voltage-Temperature コーナをまたいで回路歩留まりを評価する Yield Multi-Corner Analysis は、各コーナで大量の SPICE シミュレーションが必要になり、計算量が組合せ的に膨らみます。 提案手法は、個別回路ごとのハイパーパラメータ調整をやめ、TabPFN の学習済み事前分布をそのまま使う in-context learning と、自動特徴選択を組み合わせて、ゼロ調整で多コーナ解析を成立させます。 4×2 から 32×2 の OpenYield SRAM で、平均 MRE 0.11% から 1.10% の精度を保ちつつ、総検証コストを 10 倍超削減し、難しいコーナでも cross-corner transfer が効くことを示しました。

TL;DR(結論)

- 25以上の Process-Voltage-Temperature コーナをまたいで回路歩留まりを評価する Yield Multi-Corner Analysis は、各コーナで大量の SPICE シミュレーションが必要になり、計算量が組合せ的に膨らみます。

- 提案手法は、個別回路ごとのハイパーパラメータ調整をやめ、TabPFN の学習済み事前分布をそのまま使う in-context learning と、自動特徴選択を組み合わせて、ゼロ調整で多コーナ解析を成立させます。

- 4×2 から 32×2 の OpenYield SRAM で、平均 MRE 0.11% から 1.10% の精度を保ちつつ、総検証コストを 10 倍超削減し、難しいコーナでも cross-corner transfer が効くことを示しました。

なぜこの問題か

半導体の歩留まり解析は、単に平均的な性能を確認すれば済む話ではありません。しきい値電圧のずれ、ドーピングばらつき、配線寄生、温度や電圧条件の違いが重なると、同じ回路でも製造ばらつきと動作条件の組み合わせによって通る個体と落ちる個体が分かれます。特に SRAM のように繰り返し構造を持つ回路では、この影響が設計の成否を左右します。

核心:何を提案したのか

提案の核は、回路ごとにモデル仕様を設計するのではなく、あらかじめ大量の回帰タスクで学習された foundation model の事前分布を使い回すことです。ここで採用しているのが TabPFN で、個別の回路に対して再学習やハイパーパラメータ探索をせず、与えられた回路データを文脈として読み込ませるだけで posterior predictive distribution を近似します。

続きはログイン/プランで閲覧できます。

続きを読む

ログインで全文を月 2 本まで無料で読めます

無料プランで全文は月 2 本まで読めます。

Related